In questo articolo vengono riassunti e descritte tutte le CPU, le loro caratteristiche ed il funzionamento, sono catalogate per ordine cronologico e suddivise per categorie.

Dedicato a coloro che si affacciano per la prima volta al mondo delle CPU

Un particolare ringraziamento va al mio amico Gionick per aver svolto la funzione di raccogliere tutte queste info che costituiscono un sorta di "Vangelo" delle CPU

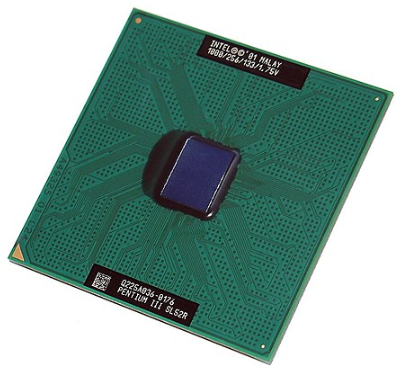

Un Intel Pentium III "Coppermine"

Microprocessore e CPU Il microprocessore è uno dei più importanti componenti del computer e anche di altri dispositivi tecnologici. In un certo senso può essere definito il vero “cervello” del prodotto tecnologico: il processore ha infatti il compito di eseguire un numero elevato di calcoli a grande velocità. È (anche) grazie al processore se un computer può eseguire tante funzioni diverse. Fino a qualche anno fa il microprocessore era una delle implementazioni più comuni della Central processing unit, la CPU per l’appunto, o Unità di elaborazione centrale. Questa è composta da tre parti principali. L’unità di controllo si occupa di leggere le istruzioni dalla memoria, esegue l’istruzione e poi se occorre memorizza i risultati stessi. L’unità logico-aritmetica invece esegue per l’appunto le operazioni di tipo logico-aritmetico. Infine ci sono i registri, che sono delle memorie molto veloci a cui si può accedere più facilmente. Oggi esistono microprocessori che assolvono tutti compiti di una CPU, e hanno al loro interno unità di controllo, unità di elaborazione fati e registri. Quindi Microprocessore e CPU, da un punto di vista teorica sono differenti ma di fatto sono diventati la stessa cosa. Funzionamento: Il compito primario di una CPU è di eseguire una serie di istruzioni chiamate solitamente programma. Per riuscire a fare ciò, ogni processore (e questo è rimasto immutato dagli anni '40 ad oggi) fa ricorso a due delle sue componenti fondamentali: la ALU (arithmetic logic unit, unità logica aritmetica) e la CU (control unit, unità di controllo). La prima è incaricata di svolgere le operazioni logico-matematiche che permettono di trasformare i dati in arrivo dalle periferiche di input, mentre la seconda ha il compito di controllare e coordinare le azioni necessarie per l'esecuzione delle operazioni. Il ciclo di lavoro di un processore è solitamente suddiviso in quattro fasi: acquisizione dell'informazione (fetch), decodifica (decode), esecuzione (execute) e riscrittura (writeback). La prima fase consiste nell'andare a recuperare le informazioni necessarie allo svolgimento dell'operazione logica. Le informazioni sono salvate nella memoria e sono individuabili grazie a un indirizzo logico specificato in un apposito registro, il Program Counter. La fase 1

Una volta che le informazioni sono state reperite, c'è la necessità di renderle “digeribili” al processore. I dati, infatti, devono essere spezzettati in unità significative per la CPU, in modo che possa portare a termine le istruzioni richieste dal programma. La fase 2 La terza fase è quella prettamente operativa. Dopo che i dati sono stati scomposti e resi “digeribili” alle unità logico-aritmetiche del processore, questi vengono trasformati in base alle operazioni che ogni programma invia al processore stesso. La fase 3 Nella quarta e ultima fase, quella della riscrittura, i dati così modificati vengono riscritti in una porzione casuale di memoria e messi a disposizione del programma che ne aveva “fatto richiesta”. Il ciclo di lavoro appena descritto determina anche la velocità del processore e ne costituisce, sostanzialmente, l'unità di misura delle performance. Maggiore sarà il numero di cicli che il processore è in grado di completare nell'unità di tempo, maggiore sarà la frequenza di lavoro (misurata in hertz). Oggi le frequenze dei processori si aggirano attorno ai 3-4 Gigahertz (Ghz) ma, per avere un’idea della potenza di calcolo complessiva, va tenuto in conto che ogni singola unità di lavoro contiene al suo interno 2 o più processori (multicore). Parametri tecnici

Ciascuna CPU ha dei parametri tecnici propri che ne descrivono capacità e applicazione. I più importanti sono il socket, il clock, il numero di core e thread, la presenza di velocità Turbo, la memoria di cache, il TDP, la TJunction e i set di istruzione inclusi.

SOCKET

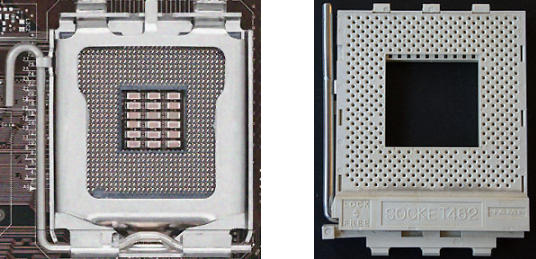

Da sinistra a destra: LGA 775 e Socket 462, 2 tipi di socket

Il socket (o zoccolo) è un connettore elettrico, fissato su una scheda madre, che permette di installare il microprocessore sulla stessa che ospita il socket esclusivamente attraverso operazioni di tipo meccanico, realizzando anche il collegamento elettrico tra i due componenti e rendendo dunque facilmente collegabile/scollegabile la CPU senza nessuna operazione di saldatura/dissaldatura. Esistono vari tipi di socket. Per quanto riguarda i microprocessori, variano a seconda della tipologia di package. SOCKET INTEL Socket 1

Processori 486 SX/DX/OverDrive 16-100 MHz

Socket 2

Processori 486 SX/DX/OverDrive 25-120 MHz

Processori Intel OverDrive 63-83 MHz

Socket 3

Processori 486 SX/DX/OverDrive 25-120 MHz

Processori Intel OverDrive 63-83 MHz

Socket 4

Processori Pentium 60-66 MHz

Processori Intel OverDrive 120-133 MHz

Socket 5

Processori dal Pentium 75 MHz al Pentium 166 MHz

Processori dal Pentium MMX 166 MHz al Pentium MMX 233 MHz con adattatore

Socket 6 (Socket derivato dal Socket 3 dopo lievi modifiche)

Ultimi processori 486 DX4 75-120 MHz

Socket 7

Processori dal Pentium 75 MHz al Pentium 200 MHz

Processori dal Pentium MMX 166 MHz al Pentium MMX 233 MHz

Socket 8

Processori dal Pentium Pro 150 MHz al Pentium Pro 200 MHz

Primissimi processori Pentium II OverDrive 300-333 MHz

Socket 370

Processori dal Celeron 300 MHz al Celeron 533 MHz - Core Mendocino

Processori dal Celeron 500 MHz al Celeron 1.1 GHz - Core Coppermine-128

Processori dal Celeron 900 MHz al Celeron 1.4 GHz - Core Tualatin

Processori dal Pentium III 500 MHz al Pentium III 1.13 GHz - Core Coppermine

Processori dal Pentium III 1.0 GHz al Pentium III 1.33 GHz - Core Tualatin

Processori dal Pentium-S III 700 MHz al Pentium-S III 1.4 GHz - Core Tualatin

Socket 423

Processori dal Pentium 4 1.3 GHz al Pentium 4 2.0 GHz - Core Willamette

Processori dal Pentium 4 1.6 GHz al Pentium 4 ? GHz - Core Northwood con adattatore

Processori dal Celeron 1.7 GHz al Celeron ? GHz - Core Willamette con adattatore

Socket 478

Processori dal Pentium 4 2 GHz al Pentium 4 2,8 GHz - Core Northwood e Prescott

Processori dal Celeron 1,7 GHz al Celeron 2,9 GHz - Core Willamette, Northwood e Prescott

Processori dal Pentium 4 1,3 GHz al Pentium 4 2,8 GHz - Core Willamette, Northwood e Prescott

Processori dal Pentium 4 EE 3,2 GHz al Pentium 4 EE 3,4 GHz - Core Prestonia e Gallatin

Socket 479

Processori Pentium M - Core Banias e Dothan

Processori Celeron M - Core Banias-512 e Dothan-1024

Socket 603 e Socket 604 (Socket utilizzati per i processori server della famiglia Xeon. Chiamati poi Xeon DP per postazioni biprocessore e Xeon MP per postazioni multiprocessore)

Processori dallo Xeon 1.3 GHz allo Xeon 3.06 GHz (Basati su Pentium 4. Chiamati poi Xeon DP per differenziarli dagli Xeon MP) - Core Prestonia

Processori dallo Xeon MP 1.4 GHz allo Xeon MP 2.8 GHz - Core Gallatin

Processori dallo Xeon DP 2.8 GHz allo Xeon DP 3.6 GHz - Core Nocona

Processori Xeon MP (2.83 GHz- 3 GHz- 3.33 GHz) - Core Potomac

Processori Xeon MP (3.16 GHz- 3.66 GHz) - Core Cranfords (Sprovvisto di cache L3)

Socket PAC418 e Socket PAC611

(Socket utilizzati per i processori server della famiglia Itanium. Il primo supportava gli Itanium ed il secondo gli Itanium 2)

Processori Itanium 1

Processori Itanium 2

LGA 775

(Intel ha fatto un grande salto passando dal Socket 478 al Socket LGA775. L'abbreviazione LGA sta per Land Grid Array e la differenza principale riguarda i pin, non più presenti sulla CPU ma spostati sul Socket della motherboard.)

Processori dal Pentium 4 2,6 GHz al Pentium 4 3,8 GHz - Core Prescott - core Cedar Mill

Processori dal Celeron 2,5 GHz al Celeron 2,9 GHz - Core Prescott

Processore Pentium 4 EE 3.4 GHz - 3,46 GHz - 3.72 GHz - Core Gallatin - core Prescott

Processori Pentium D da 2.8 GHz a 3.4 GHz - Core Smithfield - Core Presler

Processori Pentium Extreme Edition - 3.20 GHz - 3.46 GHz - 3.72 GHz - Core Smithfield - Core Presler

Processori Intel Core 2 Duo(1.60 GHz - 3.33 GHz) - core Conroe - core allendale - Core Wolfdale

Processori Intel Core 2 Extreme (2.66 GHz - 3.20 GHz) - core Conroe - core Kentsfield - core Yorkfield

Processori Intel Core 2 Quad (2.33 - 3.00 GHz) - core Kentsfield - core Yorkfield

Socket 771

(Analogo al socket 775, anche questo nuovo socket dedicato agli Xeon di ultima generazione sarà senza i pin di contatto. Sostituisce i Socket 603 e 604.)

Processori Xeon DP serie 50xx - Core Dempsey

Processori Xeon DP serie 51xx - Core Woodcrest

Socket M

Processori Core 2 Duo

Processori Core Duo

Processori Pentium Dual-Core

Processori Core Solo

Processori Celeron M

Processori Celeron

Socket P

Processori Core 2 Duo destinati ai portatili delle piattaforma Centrino Pro Santa Rosa - Core Merom

Processori Core 2 Quad

Processori Pentium Dual-Core

Processori Celeron M

Socket B

(Nome commerciale LGA 1366.)

Processori Core i7: Bloomfield, Xeon DP Gainestown e basati su architettura Nehalem.

LGA 1155

Processori basati su architettura Sandy Bridge e Ivy Bridge

LGA 1156 (ex LGA 1160)

Processori Core i3 e Core i5 di tipo:

Desktop Lynnfield e Havendale, mobile Clarksfield e Auburndale, basati su architettura Nehalem in commercio dalla fine del 2008.

Socket H

Processori (mai sviluppati) basati su architettura Nehalem.

Socket LS

(Nome commerciale LGA 1567)

Processori Xeon MP Beckton basati su architettura Nehalem in commercio dall'inizio del 2009.

Socket 1150

Processori basati su architettura Haswell

Socket 2011

Processori basati su Sandy Bridge-E e Ivy Bridge-E

LGA 1151

Processori basati su Skylake (Kaby Lake, Coffee Lake, Cannon Lake)

LGA 3647

Processori basati su Xeon Phi

LGA 2066/Socket R4

Processori Skylake-X e Kaby Lake-XSOCKET AMD Socket 1 Processori Am5x86 133 con adattatore

Socket 2

Processori Am5x86 133 con adattatore

Socket 3

Processori Am46 DX4 120 MHz

Processori Am5x86 133

Socket 5

Processori dall'AMD K5 75 MHz al K5 166 MHz

Processori dall'AMD K6 166 MHz al K6 333 MHz

Processori dall'AMD K6-2 266 MHz al K6-2 400 MHz

Socket 7

(Chiamato anche Super Socket 7 per non confonderlo con la controparte Intel. Aveva la stessa pedinatura del Socket 7 ma supportava anche l'AGP e un clock maggiore.)

Processori dall'AMD K5 75 MHz al K5 200 MHz

Processori dall'AMD K6 166 MHz al K6 300 MHz

Processori dall'AMD K6-2 266 MHz al K6-II 550 MHz

Processori dall'AMD K6-2 plus 450 MHz al K6-II+ 550 MHz

Processori dall'AMD K6-III 400 MHz al K6-III 550 MHz

Processori dall'AMD K6-III plus 450 MHz al K6-III+ 550 MHz

Socket 462

(Conosciuto come Socket A. Famoso per la lunga vita. Creato nel 2000 e abbandonato definitivamente a metà 2005.)

Processori dall'Athlon Classic 650 MHz al 1,4 GHz - Core Thunderbird

Processori dal Duron 600 MHz al Duron 950 MHz - Core Spitfire e Morgan)

Processori dal Duron 900 MHz al Duron 1,8 GHz - Core Applebread

Processori dall'Athlon XP 1500+ all'Athlon XP 2100+ - Core Palomino

Processori dall'Athlon XP 1700+ all'Athlon XP 2100+ - Core Thoroughbread step A

Processori dall'Athlon XP 1700+ all'Athlon XP 2800+ - Core Thoroughbread step B

Processori dall'Athlon XP 2200+ all'Athlon XP 2700+ - Core Thorton (un Barton con cache di secondo livello dimezzata)

Processori dall'Athlon XP 2500+ all'Athlon XP 3200+ - Core Barton

Processori dal Sempron 2200+ al Sempron 3000+ - Core Thoro-B e Barton

Socket 563

Processori dall'Athlon XP-M 1900+ all'Athlon XP-M 3000+ - Core Thoro-B

Processori dall'Athlon XP-M (Low-Power) 1400+ all'Athlon XP-M (low-Power) 2200+ - Core Thoro-B

Socket 940 (Probabilmente il Socket AMD che ebbe vita più breve in ambito Desktop. Esiste ancora in ambito server per processori Opteron.)

Processori dall'Athlon 64 FX-51 all'Athlon 64 FX-53 - Core SledgeHammer

Processori Opteron -Core ClawHammer

Socket 754

Processori dall'Athlon 64 2800+ all'Athlon 64 3700+ - Core ClawHammer e NewCastle

Processori dal Sempron 2600+ al Sempron 3300+ - Core PAlermo

Processori Turion

Socket 939

(Per il Socket 939, il successore del 940, ci sono quattro differenti versioni di CPU.)

Processori dall'Athlon 64 3000+ all'Athlon 64 4000+ - Core ClawHammer, NewCastle, Winchester e Venice

Processori dall'Athlon 64 FX-53 all'Athlon 64 FX-60 - Core ClawHammer, San Diego

Processori Athlon 64 X2

Socket AM2

Processori Athlon 64 X2, con supporto per memorie DDR2

Socket AM2+

Processori Phenom, Quad/Triple/Dual Core

Socket AM3

Processori Phenom II Quad/Triple/Dual Core, con supporto per memorie DDR3

Socket FM1

APU Llano Quad/Triple/Dual Core, con supporto per memorie DDR3

Socket FS1

AMD Llano Processors

Socket AM3+

FX Vishera, FX Zambezi, Phenom II, Athlon II e Sempron

Socket FM2

APU Trinity Quad/Dual Core

Socket FM2+

APU Kaveri and Godavari

Socket L1

(Chiamato anche Socket F o Socket 1207 per ricordare il numero di contatti, sarà il primo socket AMD ad adottare la tecnologia LGA, ovvero con i pin di contatto direttamente sul socket.)

Viene utilizzato nei processori server Opteron X2 con controller di memoria DDR2.

Socket AM1

Precedentemente chiamato FS1b, comprende una classe di CPU che contengono sia una GPU e sia un chipset integrato, formando una completa implementazione SoC.

Socket AM4

Processori basati Ryzen 7, Ryzen 5 e Ryzen 3

Socket SP3

Processori basati EPYC

Socket

Processori basati EPYC e Ryzen ThreadripperVelocità di clock Intel Turbo Boost e AMD Turbo Core

Numero di Core

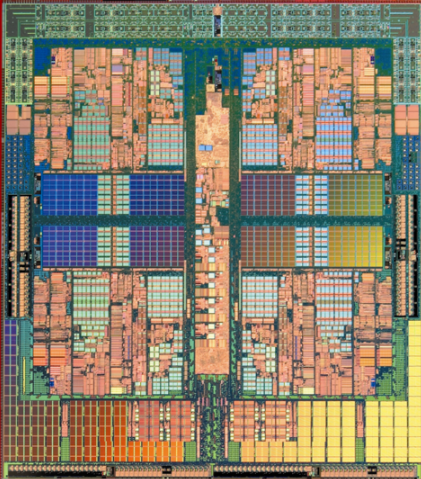

Die shrink di un AMD Phenom Quad-Core; si noti la struttura a 4 nuclei di processazione logica

Numero di thread Memoria di cache VCore TJunction e TCase

l'Intel 80387

Un Intel Pentium 4 HT, una delle prime CPU ad avere l'SSE2

Un Intel Core i7-2600K, una delle prime CPU ad avere l'AVX L'AVX (abbr. Advanced Vector Extension) è un set di istruzioni sviluppato da Intel e integrato per la prima volta nelle CPU basate sull'architettura Sandy Bridge di 2° generazione. L'AVX prevede l'introduzione di vettori a 256 bit capaci di ottenere un raddoppio dei calcoli in virgola mobile e migliorare l'organizzazione dei dati, rendendola più efficiente; le istruzioni a 128 bit vengono comunque eseguite sfruttando la metà inferiore dei nuovi registri. L'FMA è un set d'istruzioni utile a eseguire operazioni di aggiunta moltiplicata (FMA). Ne esistono 2 varianti, l'FMA4 (incluso nelle CPU AMD dall'architettura Bulldozer e realizzato nell'hardware prima dell'FMA3) e l'FMA3 (incluso nelle CPU AMD dall'architettura Piledriver e in quelle Intel dagli Haswell e Broadwell, introdotte nel 2014). L'F16C è un set d'istruzioni capace di convertire dati in mezza precisione con altri in formato standard IEEE a singola precisione con virgola mobile. I Bit Manipulation Instructions Sets (BMI sets) sono estensioni del set d'istruzioni x86 incluso nei microprocessor prodotti da Intele AMD. L'obiettivo di questi set d'istruzioni è quello di migliorare la velocità di gestione dei bit. Tutte le istruzioni di questi set operano solo in registri generici. Ci sono 2 set pubblicati da Intel: BMI (chimato anche BMI1) e BMI2; essi vennero entrambi presentati con la microarchitettura Haswell. Altri 2 set vennero pubblicati da AMD: ABM (Advanced Bit Manipulation, un subset d'istruzioni dell'SSE4a implementato da Intel con l'SSE4.2 e il BMI1) e il TBM (Trailing Bit Manipulation, un'estensione introdotta con le CPU Piledriver come estensione della BMI1, ma successivamente abbandonata nelle Zen). Le Intel SHA Extensions sono delle estensioni del set d'istruzioni x86 che apportano accelerazione hardware alla famiglia Secure Hash Algorithm (SHA). Introdotte per la prima volta con la microarchitettura Goldmont. Lista delle CPU Intel (settori Desktop e Mobile, alcuni Server)

P5

Il Pentium (nome in codice P5) è un microprocessore Intel con architettura x86 di quinta generazione che arrivò sul mercato il 22 marzo 1993, come successore dell'Intel 80486. Così come era già avvenuto in passato, Intel inizialmente pensava di continuare la numerazione progressiva indicando questo processore come Intel 80586, o i586, ma siccome i numeri non possono essere registrati come trademark, nel 1992 Intel affidò ad una società specializzata, la Lexicon Branding, il compito di coniare un nuovo nome per il processore di quinta generazione. Volendo rimarcare anche nel nome la generazione del processore, questo divenne efficacemente "Pentium" (dato che il prefisso pent, in greco, significa proprio cinque).

L'architettura P6 è stata una pietra miliare nella storia della Intel. Si trattava di un'architettura x86 di sesta generazione, derivata dalla P5, che nelle intenzioni iniziali doveva essere alla base di una CPU che avrebbe sostituito il Pentium. In realtà questo non avvenne mai e il Pentium Pro, rilasciato il 1º novembre 1995, venne indirizzato esclusivamente al settore server e workstation. L'importanza dell'architettura P6 diventa chiara se si considera che da essa sono derivati i successivi Pentium II, Pentium III e Pentium M. Il Pentium Pro utilizzava il socket 8 per collegarsi alla motherboard e, a dispetto del nome, era molto differente dal Pentium. L'architettura P6 infatti, supportava l'esecuzione out-of-order e l'esecuzione speculativa delle istruzioni, la rinominazione dei registri e possedeva una pipeline aggiuntiva per istruzioni semplici. Il Pentium Pro aveva in dotazione una memoria cache di 256 KB e 512 KB, e più tardi fu rilasciata una versione con 1 MB. Le prestazioni relative al codice a 32 bit erano eccellenti; tuttavia il Pentium Pro era più lento di un normale Pentium nel far girare codice a 16 bit, deludendo molti utenti domestici, data la predominanza a quel tempo del DOS e di Windows 3.1, interamente a 16 bit. Windows 95 era già stato rilasciato quando fu lanciato il Pentium Pro, ma la maggior parte delle applicazioni per Windows ed alcune parti dell'OS stesso erano ancora a 16 bit. Il Pentium Pro era cloccato a velocità di 150, 166, 180 o 200 MHz con un bus a 60 o 66 MHz. Molti utenti scelsero di portare il processore in overclock, portando la versione a 200 MHz a 233 MHz, e la 150 MHz a 166 MHz. Questo processore fu molto usato per architetture SMP multiprocessore, e server e workstation con due o quattro Pentium Pro divennero piuttosto comuni. Katmai, Coppermine, Tualatin

Il Pentium III fu un microprocessore x86 sviluppato da Intel come successore del Pentium II, e arrivò sul mercato il 26 febbraio 1999; al pari del suo predecessore era basato sull'architettura P6. Le prime versioni erano molto simili ai Pentium II: la maggiore differenza era il supporto delle istruzioni SSE e l'introduzione, nelle prime versioni, di un numero di serie univoco; tale caratteristica venne rimossa poi nei modelli successivi a causa delle proteste del pubblico che vedevano in tale codice identificativo una possibile violazione della privacy. A partire dalla seconda generazione del Pentium III venne anche abbandonato lo Slot 1 per la connessione del processore alla scheda madre, in favore di un ritorno ad un socket di tipo tradizionale, il Socket 370.

Netburst

NetBurst è la microarchitettura erede della P6 prodotta da Intel dal 1995 al 2001. Il primo core ad essere basato su questa architettura fu il Willamette, uscito a fine 2000. Fu il primo nella linea Pentium 4 che avrebbe adottato unicamente l'architettura NetBurst, assieme ad alcuni Celeron. Questa architettura fu sviluppata in un periodo in cui si credeva che per aumentare le prestazioni si dovesse aumentare la velocità di clock, per cui avrebbe dovuto raggiungere 10 GHz grazie a pipeline molto lunghe che, nella loro ultima incarnazione, erano arrivate fino a 31 stadi. Pipeline così lunghe subiscono penalizzazioni elevatissime in caso di salti non predetti correttamente o in caso di istruzioni che devono fermarsi per la mancanza di qualche risorsa, per cui NetBurst implementava più tecniche possibili onde evitare o minimizzare al massimo questi inconvenienti; tra queste ricordiamo l'Hyper Pipelined Technology (la speciale pipeline precedentemente descritta), il Rapid Execution Engine (che faceva lavorare la ALU a un clock doppio rispetto a quello del core) e la Execution Trace Cache (che memorizzava le operazioni dopo essere state decodificate permettendo alla CPU di richiamarle in una periodo di tempo minore).

Il Pentium D è stato il primo processore dual core prodotto da Intel dedicato al settore Desktop. Nella sua prima versione era basato sul core Smithfield, che venne poi sostituito dalla propria evoluzione, Presler. La sua caratteristica principale risiedeva nel fatto di essere il primo processore dual core commercializzato da Intel, e il suo lancio venne seguito dopo solo pochi giorni da quello dell'Athlon 64 X2 prodotto da AMD. Al momento del lancio di tale CPU, erano ormai due anni che le frequenze dei processori erano praticamente ferme. AMD aveva abbandonato la "corsa ai GHz" già da diverso tempo e Intel si era trovata costretta a fare altrettanto, migliorando l'efficienza dell'architettura e sviluppando il calcolo parallelo. In fondo la strategia intrapresa si basava su una considerazione piuttosto semplice: se non si riesce ad aumentare la velocità con cui si esegue un'operazione, per aumentare le prestazioni bisogna aumentare il numero di operazioni che si possono compiere nell'unità di tempo, e il continuo affinamento dei processi costruttivi e la miniaturizzazione consentirono di imboccare questa nuova via. Il primo Pentium D arrivato sul mercato era basato sul Smithfield, che fondamentalmente era formato da due core Pentium 4 Prescott integrati nello stesso package. Aveva una cache L2 di 2 MB equamente suddivisa tra i 2 core, e possedeva tutte le tecnologie precedentemente contenute in Prescott, tra cui il processo costruttivo a 90 nm e le istruzioni SSE, SSE2, SSE3, EM64T e SpeedStep. Nella versione Pentium Extreme Edition veniva integrato anche l'HT. Il successore di Smithfield fu Presler, arrivato sul mercato nel gennaio 2006. Era costruito a 65 nm ed era il primo processore Intel dual core con i due core distinti sul package. Le frequenze erano più alte di Smithfield, dai 2,8 GHz ai 3,4 GHz inizialmente, ma successivamente ne venne presentata una versione a 3,6 GHz. Fu l'ultimo core di architettura NetBurst. Intel Core Microarchitecture

L'Intel Core Microarchitecture è l'architettura di ottava generazione sviluppata per i processori Intel come sostituta della vecchia NetBurst alla base dei Pentium 4 e Pentium D. L'architettura "Core" è arrivata sul mercato a luglio 2006 attraverso i processori Core 2 Duo e Core 2 Extreme conosciuti con il nome in codice di Conroe e Merom, seguiti dalle relative Xeon del settore server. L'architettura "Core" affonda le proprie radici nella filosofia alla base del progetto Banias, il primo Pentium M delle piattaforme Centrino, il primo progetto in cui Intel si è preoccupata di ottimizzare il consumo energetico pur mantenendo un elevato livello di prestazioni. La prima versione della piattaforma "Core" era basata su processori dual core costruiti a 65 nm. Successivamente, a fine 2007 sono arrivati i primi processori a 45 nm, Penryn, Wolfdale e Yorkfield, che continuano ad essere basati sull'architettura "Core", sebbene in una versione rivista e migliorata, chiamata da Intel come "Enhanced Intel Core Microarchitecture". La nuova architettura "Core" ha visto l'introduzione di 6 grandi innovazioni rispetto al passato, unificando le caratteristiche del Core Duo Yonah con quelle del precedente Prescott:

Nehalem

Nehalem è il nome di una microarchitettura progettata da Intel per succedere alla precedente Core. Un sistema di anteprima con 2 processori Nehalem venne mostrato all'Intel Developer Forum nel 2007 e i primi processori ad essere rilasciati con la nuova architettura furono i Core i7 dedicati al settore desktop, nel novembre 2008. La prima generazione Intel Core prevedeva l'utilizzo di Nehalem per i soli modelli i7 e i5, dato che l'i3 sarebbe stato presentato con le successive Westmere e Sandy Bridge.

Nehalem è un nome in codice riciclato da Intel e si riferisce al Nehalem River. E' un'architettura radicalmente differente rispetto a NetBurst, della quale conserva poche caratteristiche minori. I processori basati su Nehalem hanno un processo produttivo a 45 nm, lavorano a velocità di clock più elevate e sono più efficienti rispetto ai Penryn di ultima generazione. Inoltre venne reintrodotto l'Hyper-threading, assieme a una riduzione di cache L2 e un aumento di cache L3 da 4–12 MB comune a tutti i core. Tra le altre caratteristiche si nota la presenza dell'Intel Turbo Boost 1.0, una cache L1 da 64 KB per core e L2 da 256 KB per core, l'integrazione degli standard PCI Express e DMI nel processore (rendendo inutile il northbridge), un controller della memoria integrato capace di supportare 2 o 3 canali di memoria DDR3 o 4 FB-DIMM2, tecnologia Vanderpool di seconda generazione, i set d'istruzioni SSE4.2 e POPCNT e pipeline lunghe da 20 a 24 stadi. Westmere

Westmere è il nome in codice dell'evoluzione dell'architettura x86 di nona generazione sviluppata da Intel per i propri processori; a differenza della prima generazione che è basata sul processo produttivo a 45 nm, Westmere è un die-shrink a 32 nm. I primi prodotti basati su tale evoluzione vennero presentati il 7 gennaio 2010. Trattandosi di un "ridimensionamento" dell'architettura precedente, Westmere vede il suo progetto molto simile a quello di Nehalem, ma introducendo qualche piccola novità, tra le quali il processo produttivo a 32 nm e il set d'istruzioni AES-NI. Sandy Bridge (2nd Generation)

Sandy Bridge è il nome in codice dell'architettura x86 di decima generazione sviluppata da Intel per i propri microprocessori andando a succedere all'architettura Westmere a 32 nm. Questa architettura ha debuttato il 9 gennaio 2011. Sandy Bridge prevede processori realizzati mediante processo produttivo a 32 nm e disponibili in varie versioni fino a 6 core e funzionanti a frequenze che raggiungono i 3,6 GHz (3,9 GHz con Intel Turbo Boost Technology). È previsto che la dotazione di cache per ogni core sia di 80 KB per la L1 (con un tempo di lettura di 3 cicli di clock), 256 KB per la L2 (8 cicli). Nonostante le somiglianze con la precedente Westmere, questa architettura necessita di un socket differente, di tipo LGA 1155. L'obiettivo principale della piattaforma è il contenimento dei consumi o meglio l'efficienza generale dell'intera architettura: le prestazioni sono incrementate senza per questo ricorrere a core di dimensioni maggiori rispetto a quelli dei processori precedenti, e inoltre una modalità denominata "Dynamic Turbo" consente alla CPU di eccedere il valore massimo previsto di fabbrica nel momento in cui il resto del sistema si trovi in uno stato particolarmente "fresco"; in tale modalità il clock viene aumentato con picchi pari al 37% per circa un minuto e mediamente con valori del 20% per tempi anche più lunghi. Tale funzionalità ricorda per molti versi la tecnologia Intel Turbo Mode introdotta nei processori basati Nehalem. Ivy Bridge (3rd Generation)

Ivy Bridge è il nome in codice dell'evoluzione dell'architettura Sandy Bridge sviluppata da Intel per i propri processori; a differenza della prima generazione che è basata sul processo produttivo a 32 nm, Ivy Bridge è un die-shrink a 22 nm. I primi processori basati su tale evoluzione sono arrivati sul mercato il 23 aprile 2012 e nei mesi seguenti sono andati progressivamente a occupare tutti i settori di mercato, desktop, mobile e server. Trattandosi di un "ridimensionamento" dell'architettura Sandy Bridge e non di un suo successore, Ivy Bridge vede il proprio progetto molto simile a quello di quest'ultima, ma introducendo anche alcune revisioni interne, tra le quali il nuovo processo produttivo a 22 nm, reso possibile grazie ai Transistor 3D. Il processo produttivo ha permesso ad Intel di potenziare maggiormente il comparto grafico rispetto alla componente CPU. Il numero di core e le frequenze rimangono fondamentalmente identiche rispetto alla generazione precedente, ovvero clock che sfiorano i 4 GHz e configurazioni multi core fino a 8 core (sebbene solo nel settore server), ma le varie ottimizzazioni introdotte hanno consentito alle prestazioni in particolari ambiti di arrivare a essere superiori anche del 20% rispetto alla precedente generazione Sandy Bridge. I processori Ivy Bridge introducono il supporto alle DirectX 11 e OpenCL 1.1, e sono dotati di almeno 16 unità shader, per arrivare alle 24 di alcuni modelli (ovvero il doppio di quanto integrato nel comparto grafico precedente); viene integrato anche il supporto al PCI Express 3.0, offrendo quindi un raddoppio di banda fino a 1 GB/s per ogni linea; è previsto il supporto fino a 16 linee, probabilmente divisibili anche in due segnali 8x per poter sfruttare configurazioni a doppia scheda video grazie alle tecnologie CrossFireX e SLI rispettivamente di AMD e Nvidia. Tali innovazioni consentirono un aumento di prestazioni in ambito grafico fino al 30%. Il socket è rimasto l'LGA 1155, già introdotto con i prodotti di fascia media basati su Sandy Bridge. Haswell (4th Generation)

Haswell è il nome in codice dell'architettura x86 di undicesima generazione sviluppata da Intel per i propri microprocessori, e distribuita dal 3 giugno 2013, andando a succedere all'evoluzione a 22 nm Ivy Bridge dell'architettura di decima generazione Sandy Bridge. Con Haswell lo scopo primario dichiarato da Intel è stato la massimizzazione dell'efficienza, più che il puro aumento delle prestazioni. Il progetto è nato appositamente per coniugare al meglio le prestazioni raggiunte con le generazioni precedenti di CPU, con i vantaggi offerti dal processo produttivo a 22 nm, ovvero la presenza di transistor 3D, che sono stati introdotti con la precedente Ivy Bridge in abbinamento al nuovo processo produttivo; essi contengono non uno ma ben tre gate. Tradizionalmente i transistor avrebbero un progetto strettamente planare, con i gate che si posizionano in piano attraverso il substrato. Con il progetto tri-gate un singolo gate è immesso sopra due gate verticali consentendo un'area tre volte maggiore per lo spostamento degli elettroni. Per questo motivo, in tutte le occasioni in cui Intel ha avuto modo di sfoggiare le qualità della nuova architettura, il confronto con il passato è sempre stato fatto in termini di consumo complessivo e potenza del comparto grafico, piuttosto che sulla potenza del processore come avveniva in passato. I core dei processori basati su Haswell hanno una pipeline a 14 stadi; il socket della fascia media è il nuovo LGA 1150 per i sistemi desktop e rPGA947 e BGA1364 per quelli mobile, mentre è stato integrato il pieno supporto allo standard PCI Express 3.0, del quale sono presenti fino a tre controller in alcuni modelli. Per quanto riguarda la cache, essa è basata su un progetto completamente innovativo; inizialmente si era parlato della possibilità di avere una L1 da 128 kB e una L2 da 1 MB per ciascun core, ma informazioni successive hanno invece confermato che è presente una tradizionale L1 da 64 kB (32 kB per i dati e 32 kB per le istruzioni) con associatività a 4 vie, una L2 da 256 kB per ciascun core, sempre con associatività a 4 vie, e una L3 (fino a 16 MB in alcuni modelli) condivisa tra tutti i core con associatività a 8 vie (ma non è esclusa, nelle versioni server, anche la possibilità di inserire fino a 32 MB di cache L3). Sono presenti 2 ulteriori unità di calcolo inedite; la prima consiste nella possibilità di integrare nei processori anche un co-processore vettoriale che si occupa dell'elaborazione di questo particolare tipo di calcoli, mentre fa il suo debutto anche un nuovo set di istruzioni (come del resto Intel ha sempre fatto anche nelle architetture precedenti), inizialmente chiamato FMA (Fused Multiply-Add), ma che a regime ha preso il nome di AVX2, che consente di effettuare simultaneamente un'operazione di moltiplicazione e una di addizione attraverso una sola istruzione. In particolare sono presenti le nuove istruzioni BMI (Bit Manipulation), e le estensioni TSX (Transactional Synchronization Extension). Il nuovo set di istruzioni AVX2 consente di raddoppiare la velocità dei calcoli in virgola mobile in singola e doppia precisione rispetto a quanto possibile con le precedenti AVX introdotte con Sandy Bridge; per ogni ciclo di clock è ora possibile eseguire 32 operazioni in singola precisione e 16 in doppia. Broadwell (5th Generation)  Broadwell è il nome in codice dell'evoluzione dell'architettura Haswell sviluppata da Intel e rilasciata tra il 2014 e il 2015; a differenza della prima generazione basata sul processo produttivo a 22 nm, Broadwell ha un die-shrink a 14 nm. Trattandosi di un "ridimensionamento" dell'architettura Haswell e non di un suo successore, Broadwell ha un progetto molto simile a quello di quest'ultima, ma con qualche piccola novità atta a ottimizzare ulteriormente l'efficienza complessiva, tra le quali il nuovo processo produttivo FinFET. Oltre al comparto grafico migliorato e al PCH, queste CPU introdussero anche i controller Ethernet, Thunderbolt e USB 3.0. Skylake (6th Generation)  Skylake è il nome in codice di un'architettura sviluppata da Intel. Il debutto ufficiale è stato a agosto 2015, andando a sostituire la precedente architettura Haswell. Esistono 4 varianti di Skylake, di cui solo una può essere montata in un tradizionale socket, l'LGA 1151: Skylake-S (SKL-S, LGA), Skylake-H (SKL-H, BGA), Skylake-U (SKL-U, BGA) e Skylake-Y (SKL-Y, BGA). In questa architettura venne abbandonata l'integrazione del Fully Integrated Voltage Regulator (FIVR) che nella precedente architettura era stato integrato direttamente nel die della CPU, al fine di contenere i consumi del processore. Altre caratteristiche sono il supporto fino a 20 linee PCI Express 3.0 e, per la prima volta, quello agli standard PCI Express 4.0, SATA Express e Thunderbolt 3.0 (mediante il controller Alpine Ridge). Le varianti SKL-U e SKL-Y supportano un solo slot DIMM per canale, mentre le varianti SKL-H e SKL-S possono ospitare 2 slots DIMM per canale, per una quantità massima di RAM DDR4 di 64 GB. A queste caratteristiche si aggiungono alcuni set di istruzioni quali AVX-512F (Advanced Vector Extensions 3.2), Intel SHA Extensions (SHA-1 e SHA-256, ovvero Secure Hash Algorithms), Intel MPX (Memory Protection Extensions) e Intel ADX (Multi-Precision Add-Carry Instruction Extensions). Kaby Lake (7th Generation)  Kaby Lake è l'evoluzione dell'architettura Skylake; al pari della generazione precedente, è basata sul processo produttivo a 14 nm e ne costituisce solo una relativamente semplice revisione. L'arrivo sui mercati dei primi processori basati su tale evoluzione è avvenuto nel 2016 con le serie Y e U destinate ad equipaggiare notebook e alcune tipologie di tablet PC. Ad esse si sono susseguite le CPU desktop, uscite nelle prime settimane del 2017. Trattandosi di una revisione dell'architettura Skylake e non di un suo successore, Kaby Lake risulta essere molto simile a quest'ultima, a partire dal socket, mentre il chipset utilizzato appartiene alla cosiddetta "Serie 200", conosciuta con il nome in codice di Union Point, pur continuando a supportare la serie precedente. Tra le novità introdotte con la nuova architettura, si segnala una nuova profonda revisione del comparto grafico integrato, per aumentare ulteriormente le prestazioni e offrire anche il pieno supporto allo standard video 4K e al sistema di protezione HDCP 2.2. Più nello specifico, è stato aggiunto il supporto nativo alla codifica video HEVC e VP9 a 10 bit, allo standard USB 3.1 e alla nuova tecnologia di memoria sviluppata da Intel, la Intel Optane. Kaby Lake Refresh, Coffee Lake & Cannon Lake (8th Generation)

L'8 agosto 2017 Intel annunciò che la nuova generazione di processori sarebbe stata rivelata il successivo 21 agosto. Anzichè presentare una nuova architettura per la nuova generazione, Intel dichiarò che l'ottava generazione sarebbe stata basata su 3 microarchitetture chiamate Kaby Lake R (dove R sta per Refresh), Coffee Lake e Cannonlake. La prima di queste ad esser stata presentata è stata Kaby Lake-R, con 4 CPU rivolte al mercato dei PC portatili a bassi consumi, e descritta nella tabella di seguito. Dopo la rivelazione delle CPU Ice Lake 10 nm+ e le CPU Kaby Lake-R destinate al settore mobile, Gigabyte annunciò che il 5 ottobre 207 sarebbero diventate disponibili le CPU Desktop basate sull'architettura Coffee Lake, la quale è fondamentalmente una seconda ottimizzazione dell'architettura Skylake e lanciata sul mercato come diretto competitore delle soluzioni Ryzen a basso costo offerte da AMD. Rispetto alle generazioni precedenti, Coffee Lake porta un incremento significativo nelle prestazioni multi-thread grazie a un aumento dei core, con il processore mainstream di punta Core i7-8700K caratterizzato da 6 core e 12 thread. - Core i7-8700K vs Core i7-7700K: +11% in Single-Thread; +51% in Multi-Thread - Core i5-8600K vs Core i5-7600K: +19% in Single-Thread; +55% in Multi-Thread - Core i3-8350K vs Core i3-7350K: +17% in Single-Thread; +65% in Multi-Thread Un autentico balzo in avanti, mantenendo il socket LGA1151 ma non la compatibilità con i chipset serie 100 e 200, rimpiazzati dalla nuova piattaforma di serie 300. Icelake (9th Generation)  Icelake è la nuova microarchitettura prodotta da Intel attraverso il processo produttivo 10nm+ che rimpiazzerà Coffee Lake e Cannon Lake tra il 2018 e il 2019. Ice Lake verrà usata assieme ai chipset Intel della serie 4xx e verrà prodotta con la seconda evoluzione del processo produttivo a 10nm (10nm+), e sarà la seconda microarchitettura Intel di questo nodo, dopo Cannon Lake. Tigerlake (10th Generation)

Tigerlake è la microarchitettura evoluta dalla Ice Lake prodotta da Intel basata sul nodo a 10nm++, e che rimpiazzerà Icelake nel 2019.

AMD

K5

L'AMD K5 è un microprocessore compatibile x86 sviluppato da AMD e introdotto nel 1995, diretto competitore dell'Intel Pentium. Nessuna versione supportava le istruzioni MMX, nonostante il processore fosse molto avanzato, e più simile ad un Pentium Pro che ad un Pentium, con un'unità di transcodifica delle istruzioni x86. Il processore era fortemente superscalare: possedeva cinque ALU, in grado di eseguire istruzioni out-of-order, ma una sola FPU, mentre il Pentium possedeva due di ognuna; il metodo di rinomina dei registri permetteva miglior lavoro in parallelo delle pipeline; possedeva una cache istruzioni di 16 KB, il doppio del Pentium, e la cache primaria era associativa a 4 vie, mentre quella del processore Intel lo era a 2. Questo processore rappresentava per AMD una possibilità di sorpasso tecnologico su Intel, ma i problemi di produzione, legati alle basse velocità di clock, e dimostrati ancora dalla BPU, quattro volte più grande di quella di Intel ma di prestazioni non superiori, vanificarono il buon design. A causa del ritardo sul mercato e delle prestazioni non del tutto soddisfacenti per il tempo non fu ben recepito dal mercato come il successore K6. La linea K5 veniva distinta in due parti, SSA/5 e 5x86, la prima tra i 75 e i 100 MHz (5K86 da P75 a P100, più tardi K5 da PR-75 a PR100); l'altra da 90 a 133 MHz. AMD utilizzò il suo PR rating per paragonare i propri processori a quelli di Intel, quindi un esemplare a 116 MHz della seconda linea era chiamato "K5 PR166".

K6

L'AMD K6 è un microprocessore compatibile x86 prodotto da AMD e distribuito a partire dal 1997. Questo processore è stato pensato in particolare per essere compatibile con sistemi già esistenti basati sul Pentium della Intel, che poteva sostituire a parità di prestazioni con costo considerevolmente minore. Questo garantì alla CPU un forte impatto sul mercato e la possibilità di competere direttamente col processore Intel. Il design del K6 fu progettato sulla base dell'Nx686, che la NexGen stava sviluppando quando fu acquistata da AMD. NexGen era intenzionata a produrre il processore con un proprio formato di socket, ma AMD impose il rispetto dello standard Socket 7 per avere maggiore compatibilità, aggiunse il supporto delle istruzioni MMX e chiamò il processore K6. Nonostante la sigla faccia pensare ad una continuità col K5, il design era completamente diverso, creato dall'azienda che poi fu inglobata. Il K6 fu lanciato a velocità di 166 e 200 MHz nell'aprile del 1997, e seguì nello stesso anno anche una versione a 233 MHz. Il rilascio della versione a 266 MHz non fu possibile fino alla primavera del 1998, quando AMD poté effettuare il passaggio al processo di produzione a 0.25 micron. L'ultima modifica fu apportata a maggio con la versione a 300 MHz prima dell'introduzione del K6-2 e del K6-III. K7 AMD K7 è la settima generazione di CPU x86 progettata e prodotta da AMD. La K7 è la prima architettura interamente progettata dalla compagnia di Sunnyvale; introduce importanti sviluppi rispetto alla 6ª generazione, tra i quali l'adozione del bus bidirezionale Alpha EV6 sviluppato dalla Digital Equipment Corporation (DEC). Tra le CPU prodotte con quest'architettura si ricordano l'Athlon Classic, l'Athlon XP, il Duron e, successivamente, il Sempron. L'Athlon Classic fu il primo processore prodotto da AMD ad adottare l'architettura K7, uscito il 21 agosto 1999. La prima versione dell'Athlon, Argon, aveva inizialmente velocità comprese tra 500 e 700 MHz in uno Slot A. Più tardi fu introdotta una revisione del core chiamata K75 (Rispettivamente i core Pluto e Orion) che riuscì ad arrivare alla soglia dei 1000 MHz grazie al nuovo processo produttivo a 180 nm e a dei voltaggi operativi leggermente aumentati, pur mantenendo la compatibilità meccanica con lo Slot A. Internamente i primi Athlon erano essenzialmente un core K6 reso compatibile col protocollo bus EV6, con miglioramenti nell'unità floating-point del K6 e una cache 2x64 KB di primo livello. Come i Pentium II e III Katmai aveva una cache L2 da 512KB esterna al chip e funzionante a 700-1000 MHz. L'Athlon Classic fu un enorme successo non solo per merito proprio, ma anche perché Intel, normalmente affidabile, incontrò in questo periodo una serie di problemi di produzione, design, e di controllo della qualità. In particolare, il passaggio di Intel al processo di produzione a 0.18 μm, che iniziò nel tardo 1999 e si svolse fino alla metà del 2000, fu caotico, e ci fu una grave insufficienza di Pentium III sul mercato. Molti produttori da tempo esclusivi Intel trovarono la combinazione delle eccellenti performance e del ragionevole prezzo dell'Athlon interessante La seconda generazione dell'Athlon, core Thunderbird, debuttò il 4 giugno 2000. Questa versione dell'Athlon uscì in formato PGA Socket 462, detto anche Socket A, pur producendo anche versioni da 650 a 1000 MHz per Slot A. La più grande differenza rispetto ai predecessori fu la cache; la cache esterna da 512 KB venne rimpiazzata con una interna da 256 KB a piena velocità. L'architettura dettò nuovi standard in quanto a prestazioni per ciclo di clock, dato che era era molto più efficiente di quella del Pentium 4 a parità di clock. Nell'ottobre 2000 fu introdotto l'Athlon modello "C", con il front side bus della scheda madre passato a 133 MHz (FSB 266) dal precedente modello a 100 MHz ottenendo prestazioni migliori di circa il 10% rispetto al modello "B". Il Thunderbird fu il processore di maggior successo di AMD in dieci anni. Le schede madri erano molto migliorate in questo periodo, e il piccolo cerchio di costruttori che supportavano l'Athlon crebbe fino ad includere tutti i maggiori produttori. Tuttavia ad aprile 2001 la situazione cambiò, il P4 1.7 GHz diede avviso che Thunderbird non avrebbe potuto mantenere la leadership delle prestazioni per molto, a causa dei problemi di calore e di consumo del design che lo rendevano incapace di superare i 1400 MHz. L'Athlon XP era un processore progettato e costruito da AMD nel 2001 per sostituire l'Athlon Classic. Il suffisso "XP" ufficialmente significa eXtreme Performance, anche se probabilmente voleva apparire particolarmente indicato per il sistema operativo Microsoft Windows XP allora prossimo all'uscita. Il primo Athlon XP, nome in codice Palomino, sbarcò sui desktop il 9 ottobre 2001 a frequenze comprese tra i 1333 e 1533 MHz. Il maggior cambiamento rispetto all'Athlon Classic fu l'introduzione delle istruzioni SSE, che permisero all'Athlon XP di guadagnare il 18% nel test SYSmark. Fu inoltre migliorato il meccanismo di prefetch dei dati rispetto a Thunderbird e venne aggiunta la possibilità di sfruttare appieno il FSB per la predizione dei dati, per cui rispetto al predecessore le prestazioni dipendevano in misura maggiore dalla velocità del FSB e della RAM. Entrambe le cache L2 utilizzavano un'architettura esclusiva, per cui i dati contenuti nella cache L1 non venivano duplicati in quella L2, permettendo di salvare un contenuto informativo più ampio. Per quanto riguarda il package, quello dell'Athlon XP fu il primo a base organica di AMD, abbandonando quello a base ceramica. Fu introdotto un diodo termico, che permetteva di misurare la temperatura della CPU con una precisione decisamente maggiore di quella offerta dai sensori della motherboard, proteggendo il core da eventuali fenomeni termici. Le migliorie di cui sopra unite ad altre minori consentirono all'Athlon XP di offrire rispetto al Thunderbird un incremento medio delle prestazioni del 10% alla stessa frequenza di clock insieme alla riduzione del consumo elettrico e quindi delle temperature a cui operava la CPU. Ad esempio alla frequenza di 1400 MHz il TDP passò dai 72,1 W dell'Athlon Classic a 62,8 W dell'Athlon XP, per una riduzione dei consumi al massimo carico pari al 14,8%. Quest'ultima mossa, insieme al package a base organica, permise ad AMD di aumentare considerevolmente il limite massimo di clock a cui poteva spingere un proprio processore. Infatti, con lo stesso TDP da 72 W Palomino raggiunse i 1733 MHz (2100+), ovvero un aumento della frequenza del 23% dai 1400 MHz dell'Athlon Classic. L'Athlon XP fu commercializzato con un sistema di PR rating, che fu concepito, almeno inizialmente, per comparare le prestazioni dell'Athlon XP con il suo predecessore. Le prestazioni dell'Athlon XP 1800+ al debutto era nell'ordine del 10% superiori a quelle di un Pentium 4 da 2 GHz, top di gamma Intel all'epoca, anche per via della mancanza di software in grado di sfruttare le potenti istruzioni SSE2 integrate nella cpu della casa di Santa Clara. Con l'avvento del core P4 Northwood, l'Athlon XP con core Palomino faticò a competere sul piano dei consumi per via del processo produttivo. La quarta generazione di Athlon, nome in codice Thoroughbred, fu messa in commercio il 10 giugno 2002 con frequenze comprese tra gli 1800 (2200+) e i 2133 MHz (2600+). Il design del Thoroughbred non differiva in alcun modo dal suo predecessore, eccetto il nuovo processo produttivo a 130 nm. AMD subito dopo il lancio del prodotto cominciò ad avere problemi di smaltimento di calore nel Thoroughbred A, che furono risolti con il pronto rilascio della versione B; gli overclocker, tuttavia, preferiva ancora il Palomino che, nonostante il processo produttivo a 180 nanometri, garantiva maggiori margini di aumento della velocità. Il Thoroughbred B risolse questo problema aggiungendo un substrato di rame nel processore che eliminava le interferenze e riuscì in questo modo a garantire l'aumento della velocità di clock dei processori e quindi il definitivo abbandono del predecessore. Tuttavia, nonostante il successo del 2600+ B, AMD non riuscì mai a garantire una buona produzione di processori 2700+ e 2800+ in grandi quantità e, all'epoca, era quasi impossibile procurarseli. Il moltiplicatore sbloccato del Thoroughbred B garantiva anche la possibilità di un underclock fino a 500 MHz con tensione di alimentazione 1,15 V e TDP di 10 Watt. Per far fronte ai problemi di disponibilità degli Athlon 2700+ e 2800+, figli dell'elevata frequenza di clock richiesta, AMD tentò di aumentare le prestazioni incrementando l'IPC, introducendo la quinta generazione, nome in codice Barton, all'inizio del 2003 con PR ratings di 2500+, 2800+ e 3000+. Nonostante non avesse frequenze di clock maggiori rispetto a quelle del Thoroughbred, guadagnò un maggiore PR rating grazie a 256KB in più di cache L2 e un FSB più rapido. A metà febbraio 2003, AMD annunciò che l'Athlon XP 3000+ sarebbe arrivato in quantità sul mercato nel mese successivo. Il modello 3200+ caratterizzato da un frequenza di 2200 MHz e l'unico Athlon XP ad avere il FSB a 400 MHz fu presentato nell'aprile dello stesso anno. Il core Thorton fu una variante del Barton con metà della L2 cache disabilitata, rendendolo funzionalmente identico al Thoroughbred B e creato per concorrere alla fascia bassa del mercato, smaltendo allo stesso tempo le CPU malfunzionanti e, naturalmente, guadagnare nella rendita di tutta la linea. In alcuni Thorton la cache disabilitata poteva essere integra e quindi riattivata con modifiche al bridge. Per quanto concerne il PR rating, vi erano diverse problematiche. In primo luogo iI core Barton era mediamente più lento di Thoroughbred e Thorton. Inoltre, anche se un Athlon XP 2800+ offriva prestazioni mediamente superiori a quelle di un Pentium 4 2,8 GHz, l'introduzione di un bus Quad Pumped a 800 MHz e della tecnologia Hyper Threading permisero all'architettura NetBust di aumentare le prestazioni alla stessa frequenza di clock, oltre ad essere nettamente migliore nelle applicazioni multi-thread. Infine, l'aggiunta di cache L2 era praticamente inutile, in quanto le grandi dimensioni della cache L1, unite all'architettura a corte pipeline e alla cache esclusiva, la lasciavano pressoché inutilizzata. Il Duron era un processore compatibile x86 fabbricato dalla AMD. Fu presentato il 19 giugno 2000 come l'alternativa di fascia bassa al processore Athlon e ai processori Pentium III e Celeron della rivale Intel. La produzione del Duron cessò nel 2004, sostituita dal Sempron. Il Duron aveva la stessa pedinatura ed ereditava tutte le capacità computazionali dell'Athlon, lavorando sulle stesse schede madri nella maggior parte dei casi. Il primo Duron era limitato a 100 MHz sul bus frontale (FSB 200), mentre l'Athlon contemporaneo poteva contare su un bus frontale a 133 MHz (FSB 266). Gli ultimi Duron disponevano di una velocità di bus frontale di 133 MHz (FSB 266) mentre gli Athlon XP correvano a 166/200 MHz (FSB 333/400). Il primo Duron, dotato del core Spitfire, fu fabbricato nel 2000 e nel 2001 con velocità che andavano dai 600 ai 950 MHz. Il core era a sua volta basato su quello dell'Athlon, Thunderbird, ridotto a 180 nm. Il Duron di seconda generazione, dotato di core Morgan, era venduto con velocità che andavano da 900 a 1300 MHz, ed era derivato dal core a 180 nm "Palomino" dell'Athlon XP. Perciò integrava molti importanti miglioramenti quali supporto completo alle istruzioni SSE della Intel, TLB più grandi, prefetch hardware dei dati e un diodo termico integrato. Diversamente dai core "Palomino", quelli "Morgan" avevano lo stesso consumo energetico dei "Thoroughbred" a causa del più alto valore di voltaggio del Duron. L'ultima generazione di Duron era chiamata Applebred, a volte "Appalbred", ed era basata sul core "Appaloosa" derivato dall'Athlon XP miniaturizzato a 130 nm Thoroughbred e mai messo in commercio ufficialmente. La più grande differenza con l'Athlon era la dimensione della cache, 64 KiB contro i 256 KiB o 512 KiB dell'Athlon. Una relativamente minima quantità di cache L2, più piccola anche dei 128 KiB della stessa cache L2 disponibile sul Celeron della Intel. Tuttavia, l'architettura delle CPU K7 godeva di una delle più larghe cache L1, ben 128 KiB. E con l'arrivo degli Athlon/Duron con zoccolo, AMD optò per un esclusivo design di cache che eleggeva la cache L1 a memoria principale, mentre la più lenta cache L2 agiva come un contenitore per i dati esondanti dalla cache L1. A causa della mancanza della duplicazione dei dati tra le due cache si poteva affermare che il Duron aveva 192 KiB di cache. Per il Celeron valeva lo stesso ragionamento con la differenza delle dimensioni più piccole: un totale di 128 KiB. Di conseguenza, l'architettura dei K7 successiva a quella basata su slot A era meno sensibile alle dimensioni della cache L2. Questa ridotta dipendenza dalla cache L2 consentì ad AMD di fabbricare cache con più latenza e meno larghezza di banda senza cali di performance. Favorendo in questo modo la diminuzione di complessità dei processori conseguentemente aumentava la capacità di produzione in fabbrica. Il Duron "Spitfire" era solo circa il 10% più lento del suo fratello maggiore, l'Athlon "Thunderbird". Duron era spesso la CPU favorita per gli assemblatori in cerca di prestazioni a basso costo. Fatto ancora più notevole, nel 2003 il Duron "Applebred" fu disponibile nelle versione con velocità di 1,4 GHz, 1,6 GHz e 1,8 GHz, tutte su un bus frontale a 133 MHz (FSB 266). Ma gruppi di appassionati scoprirono che questi Duron erano CPU con core Thoroughbred A/B, ma con cache disabilitata (forse perché difettosa). Studiando e provando essi trovarono che "Applebred" poteva essere trasformato in "Thoroughbred" con 256 KiB di cache, specialmente quelli con il core "Thoroughbred B". Tuttavia, questo fu reso possibile solo per le CPU fabbricate in un periodo di circa 4 settimane, perché dopo poco che Applebred fu immesso nel mercato la AMD cambiò il sistema di configurazione del chip con uno che non consentiva modifiche. K8 AMD K8 è l'ottava generazione di CPU x86 (successiva alla K7) AMD. K8 rappresenta la prima implementazione dell'architettura AMD64 64-bit (x86-64). I cambiamenti più radicali consistono nell'inserimento delle istruzioni x86-64 e l'integrazione del controller di memoria direttamente nel die del processore, eliminando il precedente northbridge. Le CPU ad essere basate su questa piattaforma sono gli Athlon 64 (inclusi quelli ad alte prestazioni denominati 64 FX), i Sempron, il Turion 64 e il Turion 64 X2. L'Athlon 64, prodotto da AMD, è stato il primo processore desktop con supporto alle istruzioni 64 bit ad avere un successo commerciale rilevante nel settore mainstream, ed è stato presentato al pubblico il 23 settembre 2003. Questo processore è parte della famiglia Athlon, rinnovata da tre varianti: l'Athlon 64, l'Athlon 64 X2 (variante dell'Athlon 64 a 2 core) e l'Athlon 64 FX (destinato al settore Enthusiast). Importante nuova implementazione dell'Athlon 64 è il controller di memoria integrato che permise di mettere in comunicazione la CPU con la memoria in modo diretto, permettendo allo stesso tempo di far funzionare il memory controller alla stessa frequenza del processore. Questa implementazione, in sostanza, abbassa di molto la latenza (tempo di risposta) delle memorie guadagnando molto in termini di prestazioni. Un'altra importante tecnologia implementata nell'Athlon 64 è il Cool'n'Quiet, derivato dal precedente PowerNow! per CPU mobile e simile allo SpeedStep delle CPU mobile di Intel, grazie al quale la CPU abbassa clock e tensione in entrata per risparmiare energia in caso di carichi di lavoro leggeri e portando il TDP da un massimo di 89 watt ad uno di appena 32 o 22 Watt (diminuendo il clock rispettivamente di 800 e 1000 MHz). Gli ultimi core ad essere introdotti in questa serie furono i core Orleans e Lima, entrambi su socket AM2, nei quali vennero apportati miglioramenti al controller della RAM DDR2 e un miglior modulo di risparmio energetico. Le CPU Athlon 64 sono state prodotte con processo produttivo a 130 e 90 nanometri. L'Athlon 64 X2 era la versione Dual Core dell'Athlon 64 prodotto da AMD su Socket 939 e AM2, riprendendone l'architettura K8 (in fase di sviluppo nota come K9). Dal punto di vista tecnico è dato dall'unione di due core Athlon 64 all'interno di uno stesso die con l'integrazione di unità di controllo addizionali. Essi condividono un controller di memoria dual channel di tipo DDR o DDR2 rispettivamente per le cpu Socket 939 e Socket AM2. Per entrambi i core la cache L1 era sempre di 128 KiB (64 per i dati e 64 per le istruzioni) mentre la L2 poteva avere 512 KiB o 1024 KiB, così come per gli Athlon 64. L'architettura prevedeva inoltre che le comunicazioni tra i due core avvenivano attraverso la System Request Interface (SRI), che inviava al core disponibile in un preciso momento una richiesta di elaborazione, il tutto all'interno del die del processore, senza dover in nessun modo accedere al bus esterno al processore. Questo schema era nettamente più prestante ed efficiente rispetto ad una comunicazione esterna mediante BUS; quest'ultimo infatti può causare un collo di bottiglia a causa della maggior latenza e della minor banda passante. Un'implementazione di quest'ultimo schema la si trova ad esempio nell'architettura del Pentium D. Sempron è una linea di processori desktop prodotti da AMD per sostituire i processori Duron e competere con i Celeron D della Intel. Le prime varianti erano basate sul Thoroughbred/Thorton Core dell'Athlon XP, con 256 KB di L2-cache e un FSB 333, ottenuto sfruttando in modalità DDR un segnale a 166 MHz. Il Sempron 3000+, introdotta più tardi, era invece basato sul Core Barton e ha 512 KB di L2-cache. L'ultimo Sempron su Socket A è stato il modello 3300+, con FSB 400. Le versioni successive (Paris/Palermo) sono versioni depotenziate dell'Athlon 64 hanno solo 128 o 256 KB di L2-cache e alcune di queste non supportano istruzioni AMD64. A parte queste restrizioni, le nuove Sempron condividono molte funzionalità con l'Athlon 64, incluso il controllo di memoria integrato “on-die” e il supporto per l'infrastruttura HyperTransport. Il Turion era il brand con cui AMD commercializzava i propri processori x86-64 mobili a basso consumo dell'architettura K8L e destinati a competere con i Pentium M, i Core e i Core 2, prodotti da Intel. I primi Turion 64 single-core erano predisposti al collegamento con la scheda madre attraverso il Socket 754 ed erano equipaggiati con 512 o 1024 KiB di cache L2, un controller di memoria DDR-400 single channel a 64 bit e un bus HyperTransport a 800 MHz, oltre ad avere funzioni specifiche dell'ambito energetico e per questo ampiamente pubblicizzate, come PowerNow!. I modelli più moderni "Richmond" erano disegnati per il Socket S1 e avevano un controller di memoria DDR2 double-channel. Il Turion 64 X2 era la versione dual-core del Turion 64 ed era stato concepito per competere con gli Intel Core e Core 2. Il Turion 64 X2 fu lanciato il 17 maggio 2005, dopo diversi ritardi. Questi processori adottano il socket S1 e hanno un un controller di memoria DDR2 integrato. Inoltre, essi possiedono diverse nuove tecnologie, come la AMD Virtualization Technology (AMD-V) e altre caratteristiche di risparmio energetico. I primi esemplari basati sui core Taylor e Trinidad erano prodotti con un processo produttivo a 90 nm, mentre i successivi Tyler avevano un die-shrink a 65 nm. Il Turion X2 Ultra (nome in codice Griffin) è stata la prima famiglia di processori AMD ad essere specificatamente sviluppata per piattaforme mobili, ed era basata sull'Athlon 64 con qualche accorgimento strutturale simile a quelli attuati sul Phenom per migliorare i consumi energetici e di conseguenza la vita della batteria. Il Turion Ultra venne rilasciato come parte della piattaforma mobile Puma a giugno 2008. Il Turion X2 Ultra era la versione dual-core del processore, prodotto con un processo produttivo a 65 nm su wafer di silicio da 300 mm. Questa CPU supportava le RAM DDR2-800 e possedeva diverse caratteristiche atte a migliorare le prestazioni delle memorie. Ciascun core era dotato di 1 MiB di cache L2 per un totale di 2 MiB, con frequenze di clock comprese tra 2.0 e 2.4 GHz e un TDP che va da 32 a 35 W. Il Turion X2 Ultra, a differenza dei precedenti Turion, implementava 3 tensioni: una per il northbridge e una per ciascun core. Ciò, assieme a diversi interruttori di fase permetteva a ciascun core di variare il proprio voltaggio e la propria frequenza indipendentemente dall'altro core e dal northbridge. Inoltre, in una manciata di millisecondi, il processore poteva passare a uno degli 8 livelli di frequenze e uno dei 5 livelli di voltaggio disponibili, adattandosi ai diversi carichi di lavoro e riducendo i consumi energetici, operando fino a un minimo di 250 MHz, con stati di ibernazione e un bus HyperTransport 3.0 con frequenza massima di 2.6 GHz, o 41.6 GB/s. Inoltre implementava diversi sensori termici sul die, con l'interfaccia SMBUS (SB-TSI), e la tecnologia MEMHOT che permetteva al processore di ridurre la temperatura delle memorie. Il Turion X2 Ultra utilizzava lo stesso Socket S1 del predecessore con uno schema di pin differente per funzionare in modo ottimale con il nuovo chipset RS780M. I core erano basati sull'architettura K8 anziché sulla K10. Il Turion II Ultra (nome in codice Caspian) è l'implementazione mobile della microarchitettura K10.5 prodotta a 45 nm e meglio conosciuta nella sua variante desktop Regor. E' un processore Dual-Core con velocità di clock di 2.5 GHz, 2 MB totali di cache L2 (1 MB per core), bus HyperTransport cloccato a 3.6 GT/s e una FPU a 128 bit, mantenendo il TDP di 35W del suo predecessore Turion X2 Ultra. Il Turion II è identico al Turion II Ultra, con l'eccezione che il Turion II possiede solo 1 MB di cache L2 (512 KB per core) e velocità di clock più basse comprese tra 2.2 GHz e 2.6 GHz. AMD Family 10h

L'AMD Family 10h, o K10, è una microarchitettura per CPU progettata e costruita da AMD per succedere alla K8. La serie per CPU desktop Phenom venne lanciata l'11 novembre 2007 come immediato successore all'Athlon 64 e ai Sempron a 64 bit. Questi microprocessori erano basati sul processo produttivo a 65 nm, per la prima volta usato su larga scala, e adottavano il Socket AM2 o AM2+. Le prime CPU di questa serie ad essere rilasciate sul settore Desktop furono i Phenom X4, seguiti dalle versioni a 3 core nel marzo 2008 e dai processori mobili di fascia media, che ricevettero lo stesso nome delle CPU ad elevate performance appartenenti alla K8, cioè Athlon X2. A tutte queste soluzioni AMD avrebbe presentato diversi successori nel 2009, attraverso i brand Athlon II e Phenom II. Le CPU per PC basate su K10 si suddividono in 3 famiglie principali. Per il settore a bassi costi erano disponibili il Sempron, l'Athlon II e il Sempron Mobile; per la classe media le l'Athlon X2, l'Athlon II X2/X3/X4 e l'Athlon II X2 Mobile; per il settore ad alte prestazioni i Phenom X3 e X4, i Phenom II X2/X3/X4/X6, il Turion II Dual-Core e il Turion II Ultra Dual-Core. I microprocessori basati su K10 includevano diverse migliorie rispetto alla precedente generazione. I più importanti erano: la possibilità di contenere fino a 6 core nello stesso die, o fino a 12 cores nel settore Server, grandi quantità di cache L3 condivisa tra tutti i core, collegamenti HyperTransport più veloci, la presenza di un controller di memoria integrato capace di operare come un unico controller dual-channel o 2 controller single-channel separati, con supporto (nelle versioni più recenti) alle memorie DDR3; inoltre, tutte le CPU K10 venivano costruite con il processo produttivo a 45 nm che rese la CPU altamente scalare. La grandezza dell'unità di calcolo in virgola mobile era stata portata a 128 bit, permettendo alla CPU di eseguire più istruzioni SSE a 128-bit per IPC. Pur essendo altamente performante, la serie K10 include diverse caratteristiche avanzate di gestione dell'energia che permettono, tra le altre cose, di impostare la frequenza di funzionamento dei core in base al loro carico, variare la tensione delle memorie indipendentemente da quella dei core. AMD Bobcat Family 14h

L'AMD Bobcat Family 14h è una microarchitettura progettata da AMD per le proprie APU e mirata al mercato a bassi consumi. Venne rivelata durante un discorso al Computex 2007 e ne venne avviata la produzione nel primo trimestre del 2011. Le CPU avevano un TDP compreso tra 1 e 18 W, con la possibilità di ridurre i consumi anche al di sotto di 1 W. I core basati su Bobcat venivano usati con GPU in delle unità di calcolo accelerato (APU) brandizzate Fusion. Le APU appartenenti a questa microarchitettura avevano supporto alle istruzioni AMD64, MMX, SSE, SSE2, SSE3, SSSE3 e SSE4A e possedevano un doppio decodificatore per le istruzioni x86, un'unità di calcolo a numeri interi con 2 ALU a 64 bit, un'unità di calcolo in virgola mobile con 2 code a 64-bit, un controller di memoria a canale singolo a 64 bit e cache L1 da 64 KiB, e 512 KiB - 1 MiB di L2. AMD Bulldozer Family 15h

L'AMD Bulldozer Family 15h è una microarchitettura sviluppata e prodotta da AMD per i propri processori, destinata al mercato desktop e server, rilasciata il 12 ottobre 2011 come successore della precedente K10. Bulldozer venne disegnata da zero, pertanto non è lo sviluppo di un processore precedente. Il core è specificatamente progettato per dispositivi con TDP compresi tra 10 e 125 W, con drastici miglioramenti nell'efficienza del prodotto sotto carichi di lavoro stressanti. I core Bulldozer supportano la maggior parte dei set d'istruzioni implementati nelle CPU Intel a loro contemporanei (incluse SSE4.1, SSE4.2, AES, CLMUL e AVX) assieme a degli altri nuovi proposti specificatamente da AMD: ABM, XOP, FMA4 e F16C. Stando a quanto affermato da AMD, queste CPU sono basate sul processo produttivo a 32 nm della GlobalFoundries, rimuovendo diversi elementi ridondanti che si degradavano in modo naturale nei comuni sistemi multicore, traendone vantaggio soprattutto dal punto di vista energetico. Le implementazioni di Bulldozer erano dedicate al mercato server (attraverso la microarchitettura Interlagos per Socket G34 a doppio chip per 16 core e Valencia su Socket C32 dedicato a chip singoli da 4, 6 e 8 core) e desktop (con Zambezi a 4, 6 e 8 core utilizzati su Socket AM3+). Bulldozer è il primo grande re-design di una CPU AMD dal 2003, quando il marchio lanciò la serie K8, e contiene 2 FPU a 128 bit compatibili con le istruzioni FMA che possono essere combinate in un'unica FPU a 256 bit con una cache L2 condivisa ogni 2 core, per cui una CPU a 16 core di questa famiglia avrebbe 8 di questi moduli, facendo vedere all'OS 2 core logici. In parole povere, questa architettura modulare consiste in diverse cache L2 multi-thread condivise e FlexFPU, che utilizzano il multithreading simultaneo, nel quale ciascun core fisico, 2 per ogni modulo, forma un solo thread, a differenza dell'Intel Hyper-Threading, dove 2 thread simultanei virtuali condividono le risorse di un singolo core fisico. AMD Piledriver Family 15h L'AMD Piledriver Family 15h è una microarchitettura sviluppata da AMD come successore di seconda generazione alla precedente Bulldozer. E' indirizzata al mercato desktop, mobile e server e viene impiegata nelle serie A, FX e Opteron di processori. I cambiamenti rispetto a Bulldozer sono incrementali. Piledriver usa lo stesso disegno modulare con miglioramenti alla predizione dei rami e nella pianificazione della FPU, assieme a un sistema di miglioramento dei consumi energetici. Ciò risultò in miglioramenti nelle elocità di clock dell'8-10% e un aumento delle performance attorno al 15% con caratteristiche energetiche simili. L'FX-9590 è circa del 40% più veloce del precedente FX-8150, soprattutto grazie alla frequenza di clock più alta. I primi prodotti a essere basati su Piledriver vennero presentati il 15 maggio 2012 con la serie di prodotti mobili APU, nomi in codice Trinity e Richland. Le versioni desktop di queste furono seguite a ottobre 2012 dalla serie FX basata sul nuovo core e dalle soluzioni Opteron per server a inizio dicembre 2012. Piledriver include diversi miglioramenti rispetto alla precedente microarchitettura Bulldozer, con multi-thread raggruppato, cicli di clock più alti, migliori IPC, temperature e consumi più bassi, la tecnologia Turbo Core 3.0, un controller di memoria più veloce, un gestore dell'hardware migliorato, supporto ai nuovi set d'istruzoni AVX1.1, FMA3, FMA4, F16C, BMI1 e TBM, una cache L1 e L2 più efficiente e TDP compresi tra 17 e 220 W. Jaguar, Puma e le APU L'AMD Jaguar Family 16h era una microarchitettura a bassi consumi progettata da AMD per l'utilizzo sulle APU destinata a succedere alla Bobcat nel 2013 e ad essere superata da Puma nel 2014. Questa microarchitettura, rispetto alla precedente, era doppiamente superscalare e veniva utilizzata su 4 linee di prodotti: Kabini, rivolta a notebook e mini PC, Temash, rivolta ai table, Kyoto, rivolta ai micro-server, e la serie G rivolta ad applicazioni embedded. Sia la PlayStation 4 che la Xbox One adottano chip basati sulla microarchitettura Jaguar, accoppiate a GPU ben più potenti rispetto a quelle vendute da AMD in accoppiata nelle Jaguar APU. I processori basati su Jaguar supportano i set d'istruzioni MMX, SSE, SSE2, SSE3, SSSE3, SSE4a, SSE4.1, SSE4.2, AVX, F16C, CLMUL, AES, BMI1, MOVBE, XSAVE/XSAVEOPT, ABM e AMD-V e rispetto alla precedente generazione aveva un incremento nella frequenza di clock del 10%, con un miglioramento del 15% nell'IPC, fino a 4 core con cache L2 condivisa, una nuova FPU a 128 bit, area del die più piccola, e un motore di codifica video integrato. La Puma Family 16h è il nome in codice della seconda generazione di APU basate su Jaguar, la cui linea Beema è rivolta ai notebook a bassi consumi, a differenza dei Mullins del settore tablet. Le principali differenze rispetto a Jaguar sono un abbassamento dei consumi della CPU a 1,2 V, riduzione dei consumi della GPU del 38%, riduzione di 500 mW di potenza nel controller di memoria e 200 mW nell'interfaccia del display, con boosting relativo al fabbisogno energetico, supporto alle istruzioni ARM attraverso un processore Cortex-A5 integrato e alle memorie DDR3L-1866. AMD Steamroller Family 15h

L'AMD Steamroller Family 15h è una microarchitettura sviluppata da AMD per la propria serie di APU, per succedere alla precedente Piledriver a inizio 2014 come la microarchitettura Bulldozer di terza generazione. Le APU Steamroller avrebbero continuati a usare i precedenti moduli dual-core come i propri predecessori, cercando di ottenere livelli di parallelismo più elevati. I miglioramenti della piattaforma si focalizzano su decodificatori delle istruzioni indipendenti su ciascun core in un apposito modulo, 25% in più rispetto alla massima larghezza di invio per thread, migliore pianificazione delle istruzioni, migliore predizione dei rami, cache più grandi e intelligenti e fino al 30% di istruzioni in più, e un controller di memoria migliorato. Un altro miglioramento rispetto ai core Piledriver era la presenza di nuovi set d'istruzioni, come quelli specifici per l'HEVC. AMD stima che questi migloramenti avrebbero aumentato l'IPC fino al 30% rispetto al core Bulldozer di prima generazione mantenendo le elevate frequenze del Piledriver a consumi energetici ridotti, con un miglioramento finale single-thread del 9% e multi-thread del 18% rispetto a Piledriver. Steamroller, la microarchitettura per la CPU, e Graphics Core Next, quella per GPU, sono unite insieme nella linea APU. Nel gennaio 2014, le prime APU Kaveri basate sul processo produttivo a 28 nm vennero finalmente rilasciate, seguite da maggio 2015 a marzo 2016 dalle nuove APU basate sul core Godavari. AMD Excavator Family 15h

L'AMD Excavator Family 15h è una microarchitettura sviluppata da AMD per succedere alla Steamroller per l'utilizzo nella linea APU. Il 12 ottobre 2011 AMD rivelò Excavator come il nome in codice della quarta generazione di CPU basate sul core Bulldozer. Le APU basate su Excavator per applicazioni mainstream vennero chiamate Carrizo e vennero rilasciate nel 2015, seguite da una versione senza GPU chiamata Toronto e indirizzata al mercato server e aziendale. Excavator è l'ultima revisione della famiglia Bulldozer, che sarebbe stata sostituita da 2 nuove microarchitetture l'anno successivo (Zen e K12). Questa architettura supporta nuovi set d'istruzioni come AVX2, BMI2 e RdRand, e possiede un controller di memoria capace di gestire RAM DDR3 e DDR4 e possiede librerie ad alta densità normalmente utilizzate dalla GPU per ridurre i consumi e le dimensioni del die, migliorando del 30% l'efficienza della piattaforma, con un IPC del 15% superiore rispetto a quello di Steamroller. Zen

Zen è il nome in codice di una microarchitettura sviluppata e prodotto da Amd per i propri processori, utilizzata per la prima volta nella serie di CPU Ryzen nel febbraio 2017. Il primo sistema funzionante basato su Zen venne dimostrato all'E3 2016 e venne per la prima volta presentato dettagliatamente a un evento separato dell'Intel Developer Forum 2016. Le prime CPU basate su Zen, chiamate in codice Summit Ridge, raggiunsero il mercato a inizio marzo 2017, seguite dalla serie Epyc per server a giugno 2017 e una serie di APU Ryzen Mobile nella seconda metà del 2017. Zen è stato disegnato a partire da zero ed è molto differente rispetto alla microarchitettura Bulldozer. I processori basati su Zen usano un processo produttivo FinFET a 14 nm e per questo sono più efficienti dal punto di vista energetico e sono capaci di eseguire una quantità significativamente maggiore di istruzioni per ciclo di clock. Venne introdotto l'SMT, una tecnologia che, analogamente alla Intel HT, permette a ciascun core di eseguire 2 threads. Il sistema di cache venne ridisegnato rendendo la cache L1 write-back. Inoltre, le CPU Zen adottano il socket AM4 che garantisce il supporto alle memorie DDR4 attraverso un disegno a SoC. La memoria e gli ingressi PCIe, SATA e USB vengono controllati da controller piazzati sullo stesso chip dei core della CPU, risparmiando energia e banda ma rendendo il die-shrink più complesso ma rendendolo adatto a soluzioni che vanno da mini PC a piattaforme high-end, come le Workstation, e i server. Stando a quanto affermato da AMD, l'obiettivo principale di Zen è quello di migliorare le performance per core attraverso una cache L1 write-back (che garantisce basse latenze e alte velocità), l'introduzione dell'SMT (simultaneous multithreading), una struttura modulare il cui blocco base è il Core Complex (CCX) (che consiste in 4 core e relative cache, e i quali vengono tenuti insieme dalla tecnologia Infinity Fabric), 4 ALUs, 2 AGU e 2 unità di calcolo in virgola mobile per core, una nuova cache più grande per le microoperazioni, clock più elevati, code di caricamento più lunghe, una migliore predizione dei rami simile a quella dell'architettura per APU Bobcat, supporto alle istruzioni SMAP, SMEP, XSAVEC/XSAVES/XRSTORS, XSAVES, CLFLUSHOPT, CLZERO, ADCX, AVX2, ADX e SHA, diverse tecnologie di risparmio energetico e il nuovo Extended Frequency Range (XFR), una caratteristica capace di overcloccare automaticamente la CPU in casi particolari andando oltre la frequenza massima prevista dal Turbo Mode. La microarchitettura Zen viene costruita su un processo produttivo FinFET a 14 nm affidato a GlobalFoundries, più efficiente rispetto ai precedenti 32 e 28 nm usati rispettivamente sulle serie FX e A. La famiglia Summit Ridge adotta il socket AM4 e fornisce pieno supporto alle memorie DDR4 con un TDP massimo di 95 W TDP per i modelli X e 65 W per tutti gli altri. Ciascun core Zen può decodificare 4 istruzioni per IPC e include una cache per le microoperazioni che alimenta 2 pianificatori destinati ai segmenti di calcolo con numeri interi e in virgola mobile. Ciascun core possiede 64 + 32 KiB di cache L1, seguita da una L2 da 512 KiB e una L3 (5 volte più veloce delle precedenti) da 1 o 2 MB. Zen 2 Zen 2 è il nome in codice del successore della microarchitettura Zen prodotta da AMD per i propri processori e destinata ad apportare un leggero miglioramento nelle istruzioni per ciclo di clock pur non essendo un salto equivalente, per portata, a quello da Excavator a Zen. Nel maggio 2017, il CEO di AMD Lisa Su annunciò che AMD avrebbe messo a punto il processo produttivo a 7 nm di Zen 2 nel 2017 per avviare la produzione delle nuove CPU nella seconda metà del 2008.

|